建模及制程研发的元件特性描述

测量需求

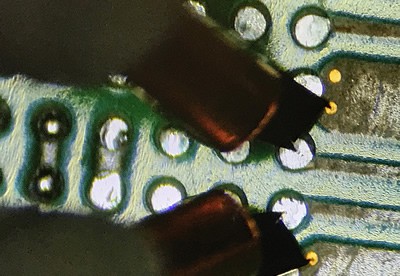

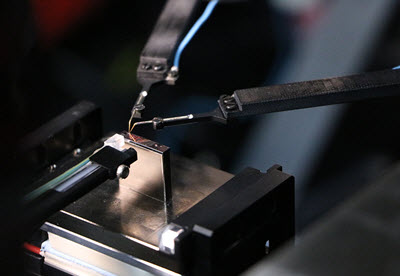

基本的元件特性描述及建模需要进行精确的 I-V/C-V、1/f、随机电报噪声(RTN)、射频、毫米波、负载拉移及噪声测量,因此在可控制温度及电磁波隔离的环境下测试是特性描述的先决条件。

典型的技术挑战包括测量重现性、下针稳定度、内部或外部噪声、探针及晶圆载台的漏电流、系统的温控性能、多重温度测试、减少系统均热时间,以及确保元件与各测试仪器间电气连接的正确性等诸多挑战。

更多数据提取的需求导致对元件特性分析的自动化程序的更多需要,因此,除了技术上的需求,通过提高测试台的效率及自动化程度成为测量的主要经济需求。

旺矽解决方案

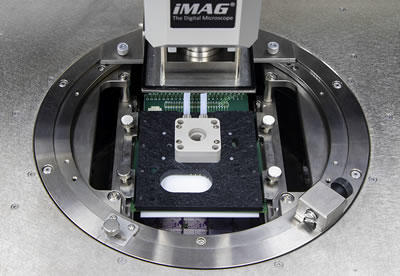

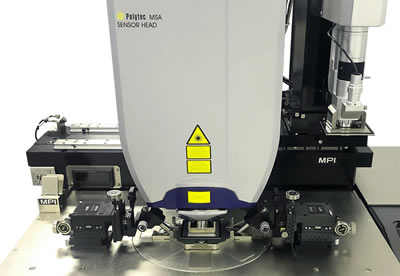

旺矽工程探针台系统旨在提供最精确、可靠的测量结果。旺矽的 TS200-SE、TS2000-SE、TS300-SE、TS3000-SE 和 TS3500-SE 探针台,皆配备电磁干扰屏蔽及光屏蔽环境 ShielDEnvironment™,另可搭配专用配件如:同轴、Kelvin、三轴测量连接的线材,低漏电高低温晶圆载台(在 -60 到 300 °C 的温度范围中,最低可达 fA 等级,且具备优异的温度均匀度)等,达成精确的元件特性描述测量。

此外,优化的测试程序、使用新型 AirCool® PRIME Thermal Chucks 高低温载台缩短系统均热时间、以及使用在冷/热状态下直接做晶圆交换,不仅缩短测试时间,同时提高测量站的测试效率,这些都是典型的旺矽解决方案。

旺矽的 WaferWallet® 亦提供 TS3500-SE 扩展至全自动化测试能力。其设计包含五个符合人体工学、便于手动上片、独立的晶圆卡匣,适合 150、200 或 300 mm 用于元件建模的晶圆。

旺矽亦提供完整的射频测量解决方案,透过旗下校正软件 QAlibria® 及 RF 探针,可在至高 110 GHz 的频率范围内协助您达到精确的射频测量及校正结果。